Е

Size: a a a

2021 July 26

Lukey. Бюджетно. Просто. У меня уже года 4 стоит мозги не делает.

AR

Из той же оперы

https://github.com/gmacario/easy-build

https://github.com/gmacario/easy-build

Е

Но кассовый чек и гарантию сохрани. Китай как никак

PB

Альтиум хорош, но действительно огромные проекты не тянет. Реюз довольно неудобный тоже. У меня пока что впечатление, что его предел по сложности проекта - небольшая материнка страниц на 50-60. И ещё один нюанс - референсы. Я пока ни разу не видел, чтобы именно в альтиуме предоставлялись исходники. Там либо импортировать, либо перерисовывать руками

А с другой стороны - у него с интерфейсом все хорошо и с batch редактированием/интеграцией с разного рода spreadsheet’ами

А с другой стороны - у него с интерфейсом все хорошо и с batch редактированием/интеграцией с разного рода spreadsheet’ами

ED

Это у Альтиума-то с интерфейсом все хорошо? :D

С интерфейсом все хорошо у DipTrace. Прозрачность слоев, все необходимые функции в контекстных меню по нажатию правой кнопки мыши, логичный набор функций.

Скажем, просто отменить трассировку дорожки/цепи в Альтиуме уже история. В DT это клик правой кнопкой на дорожку - > "Unroute trace" либо "Unroute net" там же. Два клика в каждом случае.

Даже сменить толщину дорожки нормально нельзя! Надо сначала начинать трассировку, потом ставить на паузу и потом менять.

И так далее. Каждое мелкое действие в Альтиуме делается неочевидно и неудобно.

В Альтиуме в контекстных меню есть все кроме того, что может понадобиться в момент их вызова.

Редактор печатных плат в Альтиуме - боль. Такое впечатление, что вернулся во времена DOS. Там до сих пор нет разделения сторон платы прозрачностью!

Я знаю, что прозрачность слоев там настраивается. Но даже в официальном чате признали, что настройки прозрачности нельзя привязать к смене шаблона отображения слоев.

С интерфейсом все хорошо у DipTrace. Прозрачность слоев, все необходимые функции в контекстных меню по нажатию правой кнопки мыши, логичный набор функций.

Скажем, просто отменить трассировку дорожки/цепи в Альтиуме уже история. В DT это клик правой кнопкой на дорожку - > "Unroute trace" либо "Unroute net" там же. Два клика в каждом случае.

Даже сменить толщину дорожки нормально нельзя! Надо сначала начинать трассировку, потом ставить на паузу и потом менять.

И так далее. Каждое мелкое действие в Альтиуме делается неочевидно и неудобно.

В Альтиуме в контекстных меню есть все кроме того, что может понадобиться в момент их вызова.

Редактор печатных плат в Альтиуме - боль. Такое впечатление, что вернулся во времена DOS. Там до сих пор нет разделения сторон платы прозрачностью!

Я знаю, что прозрачность слоев там настраивается. Но даже в официальном чате признали, что настройки прозрачности нельзя привязать к смене шаблона отображения слоев.

PB

Мне просто любопытно. Буквально вчера у меня была необходимость вбить задержки/длины для 350 выводов FPGA (внутренние для микросхемы). Ушло может минут 30. Это в альтиуме. Для Cadence я бы просто скачал с интела готовое УГО, где все уже содержится (и даже больше, так как у альтиума ещё и своя дурацкая специфика с FPGA).

DT, лично для меня, вообще хз что :D

Но вот как там такую задачу решить?

DT, лично для меня, вообще хз что :D

Но вот как там такую задачу решить?

KA

В последнее время часто стали появляться несложные референс платы в альтиуме с предоставлением всего исходного проекта. Сам я альтиум не особо люблю

ED

Надо погуглить. Я никогда не занимался столь масштабным выравниванием длин в DT. Но наверняка в свежем релизе там что-то есть для этого.

Впрочем, вы сами ответили на свой вопрос - для этой задачи есть Cadence. :) А Альтиум косоват со всех сторон - в нем геморройно делать и простые платы, и сложные.

Впрочем, вы сами ответили на свой вопрос - для этой задачи есть Cadence. :) А Альтиум косоват со всех сторон - в нем геморройно делать и простые платы, и сложные.

ED

И часто вы, кстати, ставите на плату FPGA с более чем тремя сотнями выводов? :)

KA

хотелось просто задержки прописать к пинам - это внутренние самого чипа

ED

А зачем это вообще для трассировки? Или вы симулировать собрались?

KA

для выравнивания как раз таки

PB

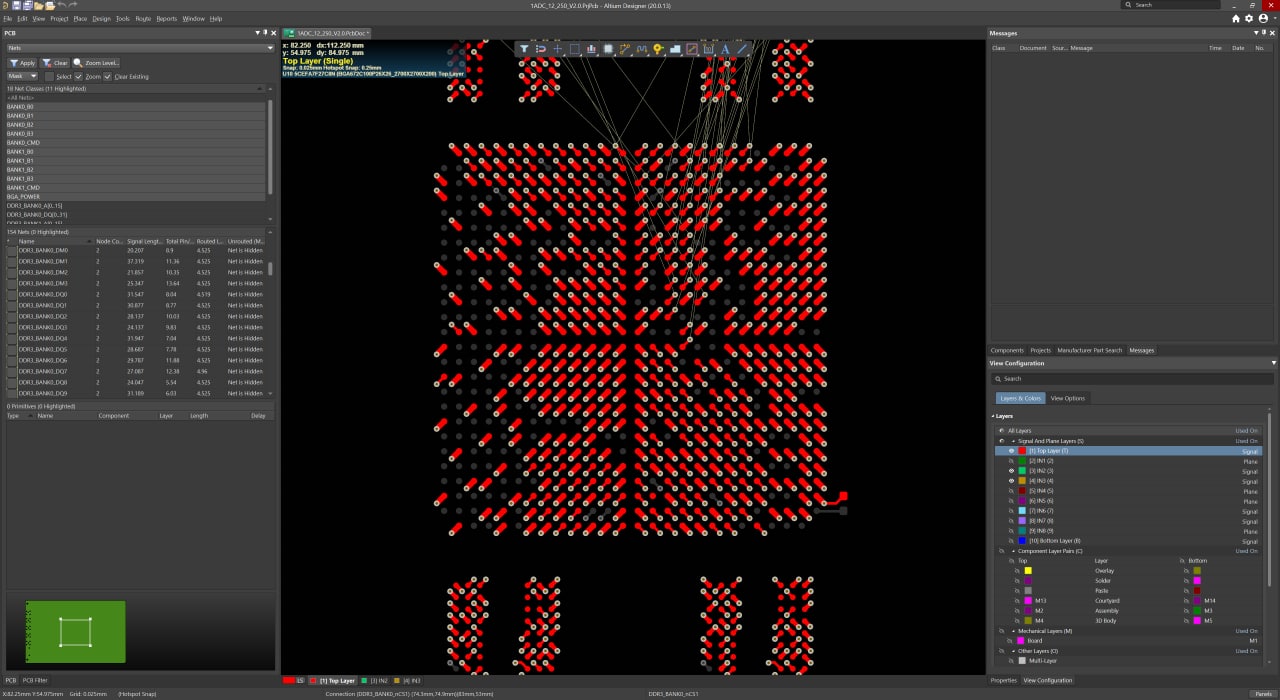

Не так чтоб масштабная задача. Я вообще разочаровался в 5 циклоне и его возможностями по работе с DDR... Но не суть. Из 672 ног почти половина на питание/землю. Мне впритык хватило на 2 банка DDR3 по 2 чипа и на 2 АЦП. Все. Там ног тупо больше не остается. Это только кажется, что вот 672 вывода это много. Ничего подобного

KA

и для симуляции тоже

PB

Ну так там внутри по сантиметру длины. Их для таймингов DDR не получится не учитывать

ED

Хм. Я обычно сначала отдельно считаю длины, и потом задаю длины дорожек непосредственно. Впрочем, если стоят задачи регулярно работать с DDR и прочими чудесами, то это к продуктам Cadence, однозначно.

PB

Благо интел задержки указывает. Вообще говоря, я не пользуюсь длинами. Вопрос же в таймингах, а тут еще и диэлектрики руками учитывать? Да ну

KA

я тоже поставил специально альтиум, чтобы попробовать развести вч девайс, но там всё убого и не удобно в этом плане, в итоге забил

ED

Я с FPGA как-то вообще мало работаю. В основном низкопотребляющие беспроводные решения. Упор на выжимание последних джоулей из батарейки, а не на пропихивание гигабит в секунду через шины в 100500 бит шириной. :)

PB

Вот это питание + 2 банка DDR. Пожалуйста :D