VK

Size: a a a

2021 February 08

Не используйте хал и проблема автоматом решится. 😁

Не решится

VK

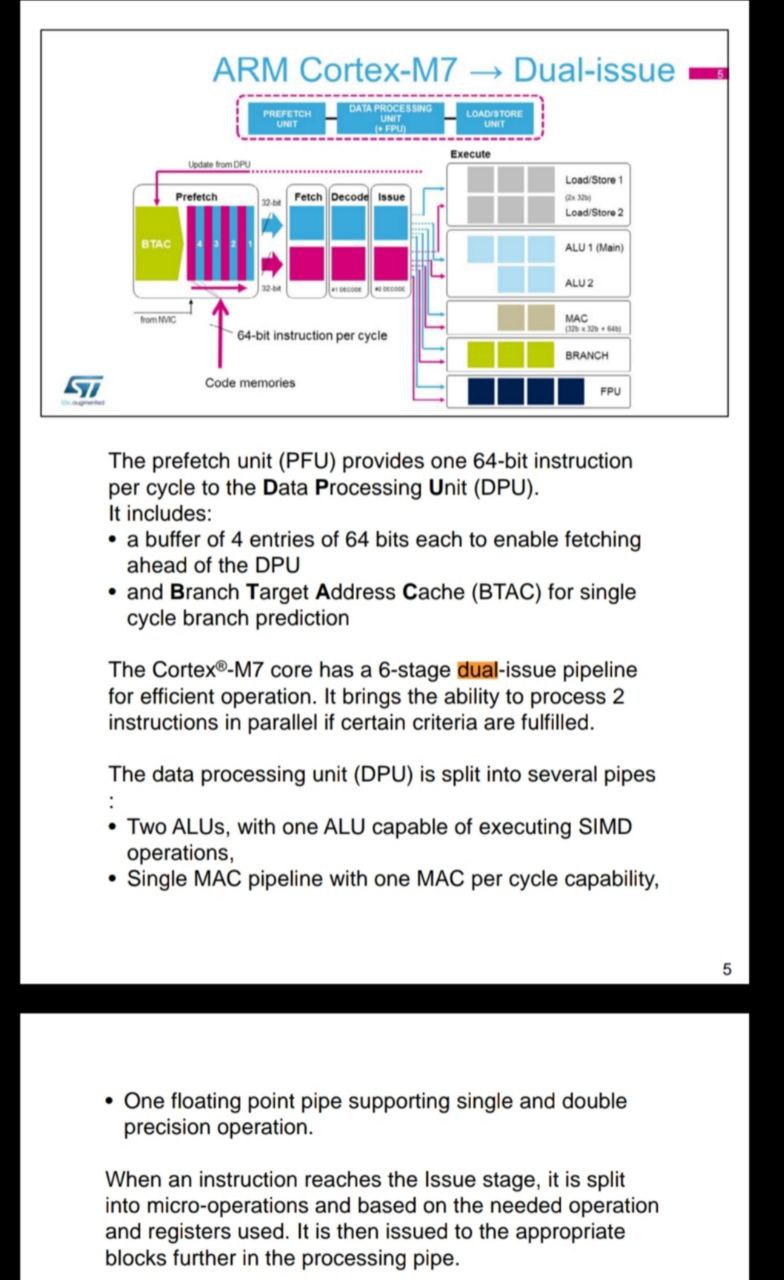

имеется ввиду двухядерное испольнение M4+M7 или что? на моем H7 нет гипертриденга..., да есть кэши, есть тессно связанная память и все такое, но гипертриденга нет есть камни с гипертриденгом? вах... можно сылку я бы почитал.

VK

Вот, на 5й странице картинка

LZ

Наверное про это речь. Про две инструкции. Но это не совсем две инструкции в параллель то

VK

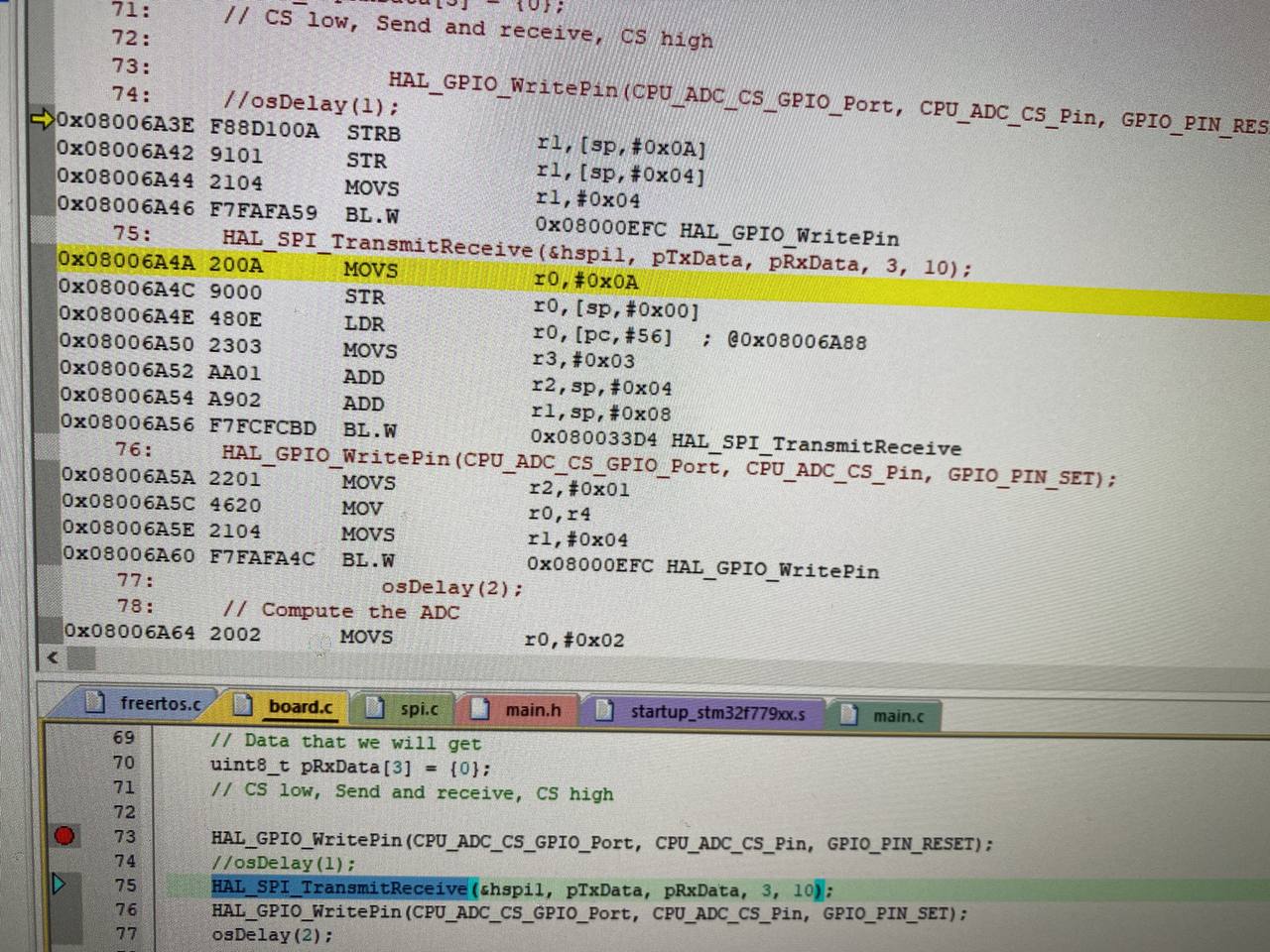

Ну я вон выше картинку кидал, когда инструкции по работе с портами и задержкой в один поток ушли, а с спи в другой

A

SIMD обычный.

VK

SIMD обычный.

Нифига, в том-то и боль

LZ

SIMD обычный.

Ну и немного спекулятивного исполнения в силу btac

Ну и загрузка двух данных, наподобие как у xtensa LX7

Ну и загрузка двух данных, наподобие как у xtensa LX7

A

Ну я вон выше картинку кидал, когда инструкции по работе с портами и задержкой в один поток ушли, а с спи в другой

Это не так, ты ошибаешься.

Там просто криво transceve написан и скорее всего нужно дождаться флажка RXNE, например, после выполнения функции

Там просто криво transceve написан и скорее всего нужно дождаться флажка RXNE, например, после выполнения функции

VK

Это не так, ты ошибаешься.

Там просто криво transceve написан и скорее всего нужно дождаться флажка RXNE, например, после выполнения функции

Там просто криво transceve написан и скорее всего нужно дождаться флажка RXNE, например, после выполнения функции

VK

где тут ошибиться? 🙂

LZ

И что мы на скриншоте должны увидеть?

VK

тут и потом в других местах я четко вижу классический race condition, когда однопоточный код начинает выполняться в более чем одном потоке. в результате на выходе херня.

A

Имплементацию функции посмотри.

Если они используют DMA - то был глюк, когда транзакция DMA считалась завершенной по передаче из памяти в периферию, а не когда фактически данные в порт ушли.

Если они используют DMA - то был глюк, когда транзакция DMA считалась завершенной по передаче из памяти в периферию, а не когда фактически данные в порт ушли.

VK

Но вообще мы начали с того, что HAL тут воду мутит и LL и прочие не стали бы так косячить :

VB

Имплементацию функции посмотри.

Если они используют DMA - то был глюк, когда транзакция DMA считалась завершенной по передаче из памяти в периферию, а не когда фактически данные в порт ушли.

Если они используют DMA - то был глюк, когда транзакция DMA считалась завершенной по передаче из памяти в периферию, а не когда фактически данные в порт ушли.

У меня у ДМА вообще прерывание не вызывалось)

LZ

Скорее что самописная либа, при достаточной квалификации - явно стабильнее иэтого поделись индусов

SK

тут и потом в других местах я четко вижу классический race condition, когда однопоточный код начинает выполняться в более чем одном потоке. в результате на выходе херня.

да какая многопотоковость. у вас просто конвеер за раз может выполнять две инструкции и все. две которые идут подрят. если вам нужны гарантии между записью в одну железку и другую ставте барьеры

A

тут и потом в других местах я четко вижу классический race condition, когда однопоточный код начинает выполняться в более чем одном потоке. в результате на выходе херня.

Это нюансы работы с периферией, а не "многопоточность"

Код исполняется инструкция за инструкцией на одном ядре.

Код исполняется инструкция за инструкцией на одном ядре.