TN

Size: a a a

2020 November 25

У них другой был, ща поищу

l

не то, но годненькое. интересно повтыкать тоже

l

спасибо! повтыкаю

l

тоже тогда закину видос полезный, правда на английском. про подавление пульсаций LDOшками https://training.ti.com/ldo-basics-power-supply-rejection-ratio-psrr

S∿

А чертеж есть? eps или ещё что векторное

Dxf есть

Y

или поднять частоту dc/dc до такой степени, что потом её просто будет задавить

В апноутах видел такой вариант: low-noise dc/dc частотой повыше и в экране -> фильтр -> ldo с низкими шумами -> умножитель ёмкости - > питание ацп и опорника, каждое со своим фильтром.

l

стандартная схема, кроме умножителя ёмкости. хм

VK

народ. кроме LDO для питания АЦП/буферов/усилков, что-то ещё в современной схемотехнике применяется для подавления пульсаций питания? если хочется максимально использовать битность ацп при питании от импульсного питальника

Что имеется ввиду под пульсациями питания?

Есть несколько механизмов влияния помех по питанию на систему (в вашем случае в итоге на SNR).

Первое - прохождение пульсаций и шумов со входа на выход источника -> см. psrr

второе - генерация шума внутри источника - ну тут понятно

третье - высокий импеданс PDN, это трассировка, подбор капов, разумное применение тех же бидов.

Есть несколько механизмов влияния помех по питанию на систему (в вашем случае в итоге на SNR).

Первое - прохождение пульсаций и шумов со входа на выход источника -> см. psrr

второе - генерация шума внутри источника - ну тут понятно

третье - высокий импеданс PDN, это трассировка, подбор капов, разумное применение тех же бидов.

l

Что имеется ввиду под пульсациями питания?

Есть несколько механизмов влияния помех по питанию на систему (в вашем случае в итоге на SNR).

Первое - прохождение пульсаций и шумов со входа на выход источника -> см. psrr

второе - генерация шума внутри источника - ну тут понятно

третье - высокий импеданс PDN, это трассировка, подбор капов, разумное применение тех же бидов.

Есть несколько механизмов влияния помех по питанию на систему (в вашем случае в итоге на SNR).

Первое - прохождение пульсаций и шумов со входа на выход источника -> см. psrr

второе - генерация шума внутри источника - ну тут понятно

третье - высокий импеданс PDN, это трассировка, подбор капов, разумное применение тех же бидов.

первое. максимально снизить пролезание пульсаций от дцдц к ацп по плате. просто я уже пару лет этой темой не занимался и думал что отстал от прогресса. но пока что поиски показывают, что с 2018 года ничего лучше high psrr ldo человечество не придумало

l

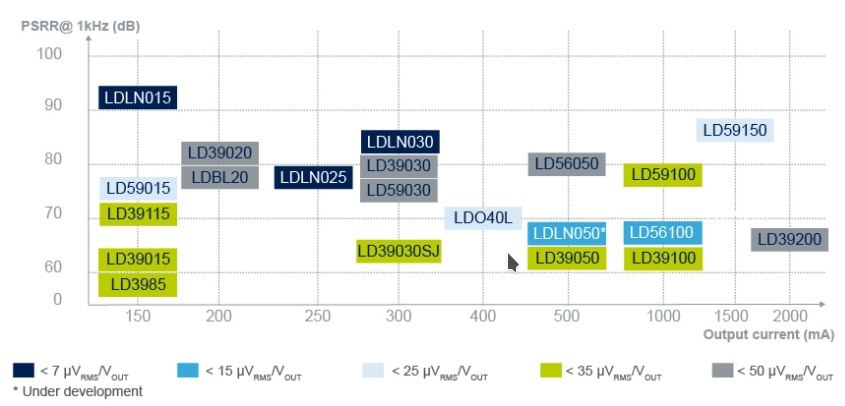

хотя сами ldoшки стали покруче

l

VK

первое. максимально снизить пролезание пульсаций от дцдц к ацп по плате. просто я уже пару лет этой темой не занимался и думал что отстал от прогресса. но пока что поиски показывают, что с 2018 года ничего лучше high psrr ldo человечество не придумало

>просто я уже пару лет этой темой не занимался и думал что отстал от прогресса.

физика не стареет, так что тут особо не дёрнешься от того, что в общем виде описывает Ярослав в своем сообщении

В апноутах видел такой вариант: low-noise dc/dc частотой повыше и в экране -> фильтр -> ldo с низкими шумами -> умножитель ёмкости - > питание ацп и опорника, каждое со своим фильтром.

Не, ну есть следующий шаг конечно, так сказать thinking out of the box: иметь буферный аккум на линии питания и в процессе измерений отключать вход от dcdc. Тогда исчезает гадящий источник и psrr уходит на второй план, но остается внутренние шумы LDO (которые таки не нулевые), ну и самое веселое — pdn

физика не стареет, так что тут особо не дёрнешься от того, что в общем виде описывает Ярослав в своем сообщении

В апноутах видел такой вариант: low-noise dc/dc частотой повыше и в экране -> фильтр -> ldo с низкими шумами -> умножитель ёмкости - > питание ацп и опорника, каждое со своим фильтром.

Не, ну есть следующий шаг конечно, так сказать thinking out of the box: иметь буферный аккум на линии питания и в процессе измерений отключать вход от dcdc. Тогда исчезает гадящий источник и psrr уходит на второй план, но остается внутренние шумы LDO (которые таки не нулевые), ну и самое веселое — pdn

l

хих. делал такое

VK

хих. делал такое

ну тогда вряд ли тут еще что-то порекомендовать можно из не-экзотики :)

VK

токи-то какие:

VK

может у вас там гигасэмплы и плисины жирные

l

около 50мА в пике