P

Size: a a a

2021 January 20

Petr Belyaev

АЦП дорогие. Конкретно у меня 850$, если штучно. Spread Spectrum позволяет рандомно варьировать выходную частоту, что размазывает электромагнитную энергию (излучаемую, что особенно важно) по спектру. В итоге пиковая спектральная мощность уменьшается. Это, в свою очередь, в целом уменьшает влияние излучателя на потенциальные антенны (антенны - это вообще любые куски металла, которые по любой причине находятся под разным потенциалом). Реализовать можно за счет VCO и "шума" на входе VCO, например. Картинка на первой странице https://www.analog.com/media/en/technical-documentation/data-sheets/6902f.pdf.

т.е. эта микросхема каждые полпериода немного изменяет длительность прямоугольника по какому-то закону?

PB

т.е. эта микросхема каждые полпериода немного изменяет длительность прямоугольника по какому-то закону?

Да, конкретно в LTC6902 это генератор всевдорандома, который заведен на внутренний ЦАП. А напряжение с ЦАПА в итоге влияет на форму модулирующего напряжения (частотная модуляция V->f за счет внутреннего осциллятора).

P

Petr Belyaev

Да, конкретно в LTC6902 это генератор всевдорандома, который заведен на внутренний ЦАП. А напряжение с ЦАПА в итоге влияет на форму модулирующего напряжения (частотная модуляция V->f за счет внутреннего осциллятора).

ясно, спасибо!

A

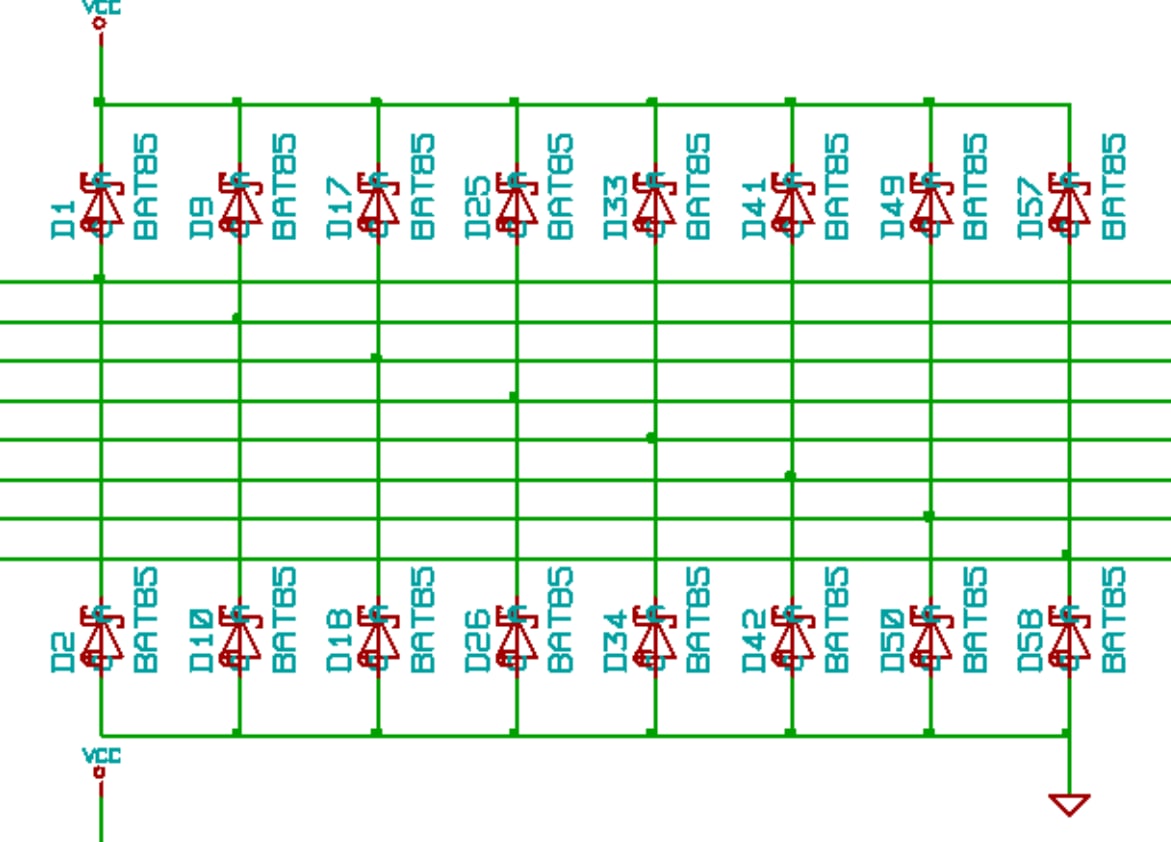

что это за диоды?

A

BAT85, диоды Шоттки

P

8-фазный выпрямитель😳

A

8-фазный выпрямитель😳

Зачем?

Это просто защита.

Это просто защита.

P

а они такие слабенькие

P

не выпрямитель)

A

Если напряжения выше Vcc или ниже Vss - излишек стекает на шину питания.

P

Если напряжения выше Vcc или ниже Vss - излишек стекает на шину питания.

пасибо, КЭП)

A

8-фазный выпрямитель😳

нет. это цепь между пьезой и входом ADC

A

ну кусочек

A

нет. это цепь между пьезой и входом ADC

Защита входа АЦП от выхода за динамический диапазон.

По сути в виде TVS-ки.

По сути в виде TVS-ки.

A

ограничитель да, как я понял

A

там размах 7-10в когда палкой лупишь

A

Petr Belyaev

Ну, прямо сейчас я допиливаю аналоговый front end с AD9625 и AD9161. Рабочие полосы 1 и 6 ГГц соответственно. Оба требуют несколько доменов питания (минимум по 2 аналоговых и 2 цифровых), каждый из которых очень чувствителен к "чистоте" питания. Таким образом, у меня возникает необходимость использовать минимум 6 BUCK конвертеров с одним входом. Переходные токи по входу у каждого из них порождают колебания входного напряжения (в зависимости от входного импеданса каждого), что частично отражается на выходе каждого. Каша. Шумов больше, если проще говорить. А вот если мы гарантируем, что силовые транзисторы внутри такой сборки не переключаются одновременно, то шума становится меньше, чего как раз можно достичь за счет разброса фаз. Это как SSN в FPGA, когда одновременное переключение кучи IO может породить ужасную электромагнитную обстановку.

К вопросу об МК - некуда. Уже FPGA + DDR + процессор. Куда еще городить? :D Хотя в другой версии этой железки все это генерировалось в FPGA.

И еще один аргумент против МК - SSFM (spread spectrum frequency modulation) там реализовывать если и можно, то не больно хочется.

К вопросу об МК - некуда. Уже FPGA + DDR + процессор. Куда еще городить? :D Хотя в другой версии этой железки все это генерировалось в FPGA.

И еще один аргумент против МК - SSFM (spread spectrum frequency modulation) там реализовывать если и можно, то не больно хочется.

Круть

A

Petr Belyaev

В итоге цель состоит в уменьшении шумов и улучшении ЭМС. В качестве референса - Henry W. Ott - Electromagnetic Compatibility Engineering. Его было бы очень долго тут пересказывать )

Buck или boost?

PB

Aleksandr Zharov

Buck или boost?

Buck. Повышать нечего, все из 12В делается. У буста еще КПД пиковый что-то около 70% вроде, так как там половину времени нужно гнать ток в землю. Может у синхронных бустов с этим лучше