A

Size: a a a

2021 June 10

d

Ну если про то что в eax кладётся, то это у каждого ядра по своему...

A

8881 (3055×1075)

A

а зачем тебе это?

DC

Чуваки, читаю “What every programmer should now about memory”. Там написано это

So the entries stored in the caches are not single words but, instead, “lines” of several contiguous words. In early caches these lines were 32 bytes long; nowadays the norm is 64 bytes. If the memory bus is 64 bits wide this means 8 transfers per cache line. DDR supports this transport mode efficiently.

When memory content is needed by the processor the entire cache line is loaded into the L1d.

Т.е. я понимаю это так:

Кеш (например L1d) хранит несколько cache entries. Каждый cache entry состоит из cache lines, который в сое очередь могут быть 64 байта

Дальше написано, что если нужно получить данные из памяти, то целая cache line загружается в L1d.

И тут я понял, что ничего не понял. Как понять логические связи между L1d, cache entry и cache line. Что их них целое, что общее? Что включает в себя другое?

So the entries stored in the caches are not single words but, instead, “lines” of several contiguous words. In early caches these lines were 32 bytes long; nowadays the norm is 64 bytes. If the memory bus is 64 bits wide this means 8 transfers per cache line. DDR supports this transport mode efficiently.

When memory content is needed by the processor the entire cache line is loaded into the L1d.

Т.е. я понимаю это так:

Кеш (например L1d) хранит несколько cache entries. Каждый cache entry состоит из cache lines, который в сое очередь могут быть 64 байта

Дальше написано, что если нужно получить данные из памяти, то целая cache line загружается в L1d.

И тут я понял, что ничего не понял. Как понять логические связи между L1d, cache entry и cache line. Что их них целое, что общее? Что включает в себя другое?

DF

есть кэш он состоит из линий

DF

если так ставить вопрос

DF

также приводится пример системной шины шириной в восьмибайтное слово

DF

для прочтения одной линии такой шине понадобится восемь загрузок

DF

но на самом деле они конечно аыполняются не последовательно

DF

там прямым текстом написано entries are 'lines'

CB

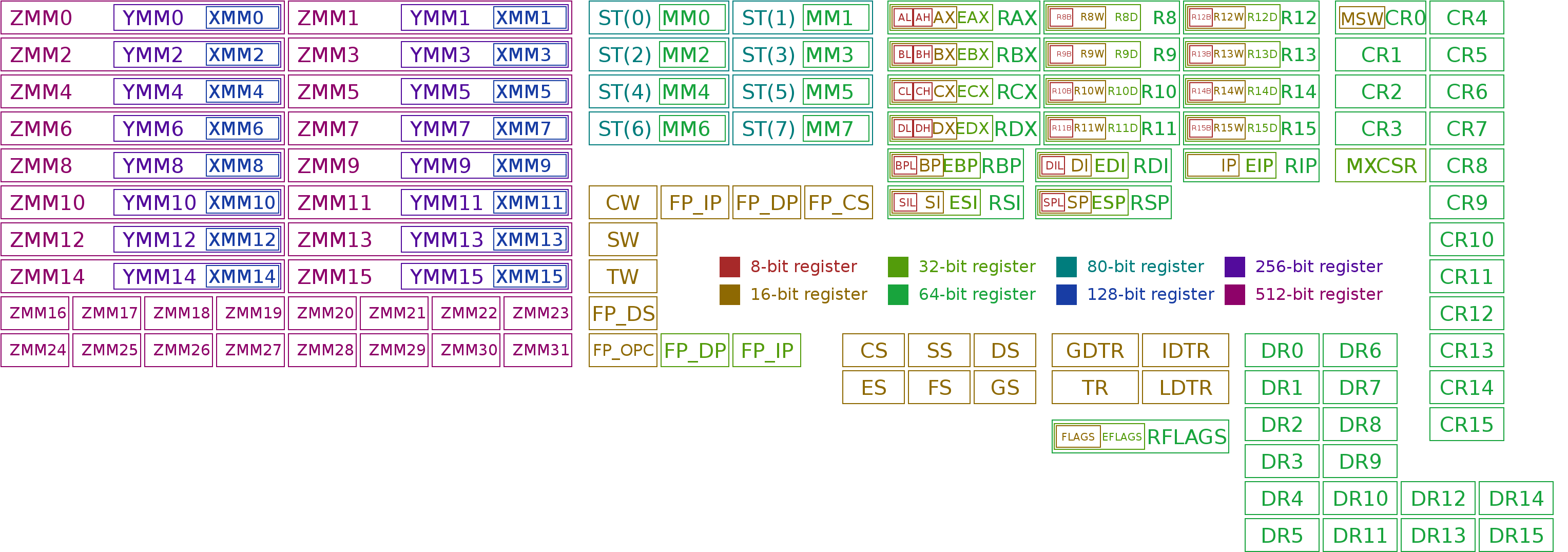

В real mode у интеловских процессоров осуществляется мап логических регистров на физические? Или условно ax будет всегда связан с одним физическим регистром под номером #1?

DF

вы про ренейминг?

DF

он всегда осуществляется емнип

CB

Да

DF

ренейминг часть пайплайна)

КК

Разве не нужно в них ориентироваться для изучения ассемблера?

CB

хотя наверное нет, я не знаю. Я помню читал что есть логические регистры которые юзаются в командах, eax и тд в интел. Но непосредственно они не привязаны к одному физическому регистру, цпу может мапить eax в разные промежутки работы в разные физические регистры

CB

эт верно?